国际电子器件会议(IEDM)通常发生在旧金山12月,但转移到一个完全在线业务在2020 -通常提供了一个方便的地方检查芯片制造业如何可能实现其长期承诺包更多的东西变成一个硅随着时间的推移而死。转向虚拟会议的同时,业界的发展方向也更加明朗。

自21世纪初以来,根据摩尔定律进行扩张就不像过去40年那么简单了,因此,摩尔定律会放缓(如果不是停滞的话)的想法一点也不令人惊讶。15年前的那次变化导致了微处理器时钟速度的突然停滞,在此之前,Dennard scale是一种标准。这规定了,只要你能在芯片表面画出越来越细的线,把晶体管做得更小不仅能让更多的晶体管被打包在一起,它们还会变得更快。

2004年以后,情况变得更加混乱,因为关于小物体的物理学开始变得更加棘手。工艺设计人员通过在硅晶格中引入应变来弥补性能提高的放缓,这有助于电子更快地移动。他们还需要处理杂散电场的影响,使晶体管在应该关闭的时候保持开着。这带来了更复杂的形状,如finFET。很快,这将被成堆的纳米带所取代。

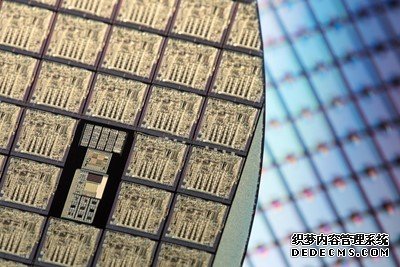

即使使用这些越来越昂贵的技巧,沐鸣测试速在晶体管成为电阻之前,晶体管通道的长度也有一个限制。虽然用于描述每一个连续过程的纳米数,如22nm, 14nm或10nm,已经符合摩尔定律,但实际的芯片尺寸要长得多。

节点名称与晶体管本身的大小已经有一段时间没有联系了。在20世纪90年代,为了提高速度,英特尔和其他公司降低了信道长度,因此节点的名称与互连的最低、最密集层的音高有关。通常情况下,你会把那个投球分成两半。即使在这里,金属半节距仍然比节点名大得多。例如,晶体管在7nm节点上的有效通道长度大约是12nm。对器件密度非常重要的金属半螺距在25nm到30nm之间。即使是所谓的1纳米节点,这个尺寸也不太可能远低于20nm,部分原因是光刻技术不能支持它,但也因为它将把电阻推到不切实际的水平。

然而,Synopsys和IEDM其他机构的分析表明,规模扩张将持续到2030年,尽管这并非一帆风顺。那么,当减少设备面积的路径逐渐被封锁时,情况又如何呢?答案就在第三个维度。这不仅仅是为了在特定容量中提供更多功能而将芯片堆叠在一起的能力。芯片内部正在进行大量的重组,以减少每个晶体管的有效面积。

Imec研究机构提出了几个想法。一种是“叉片”,它将逻辑单元中使用的两种互补型晶体管组合成一棵树状结构。这将一次性减少30%的有效面积。

必须为逻辑单元提供电源和地线,这就占用了宝贵的区域,可以用来路由逻辑信号。在这里,第三维度提供了一个答案。在2018年超大规模集成电路(VLSI)研讨会上,Imec提议将大量的轨道埋在硅表面下。他们的下一步是cet:一种两层的结构,将一个晶体管放在另一个晶体管的一半上,比forksheet更进一步。现在,你或多或少拯救了一半的区域。

在2020年的IEDM上,英特尔的工程师描述了他们对基于纳米片的cfet型结构的看法。这个想法正在流行起来。根据Synopsys的计算,cet结构对用于片上存储器的静态存储单元起了很大作用,尽管需要一些电路设计的微调才能使其工作。例如,最紧凑的结构需要虚拟晶体管之类的东西来正常工作。这样的变化将意味着SRAM密度的提高可以跟上逻辑电路的步伐,沐鸣测速地址而不是像存储器那样落后近十年。

Synopsys团队称,电路和工艺设计师之间的加强合作似乎有望保持长期的增长速度,即每两年或多或少翻一番。这一切都是有代价的。未来10年,由于这些新工艺的复杂性,以及部署这些新工艺所需的一些设备成本高得令人难以置信,每个晶圆节点的成本将平均上升13%。

即便如此,由于密度的提高,这也意味着芯片制造商将在同样的时间框架内实现每个晶体管、每个节点的成本降低30%。除此之外,你还有一个问题,那就是证明晶体管密度为每平方毫米10亿的芯片的设计成本高达数十亿美元,这使得它更像是一场只有那些财力雄厚的人才能玩的游戏。

考虑到所有这些因素,摩尔定律似乎在未来10年内都是可行的。